## **Cambridge International Examinations**

| Cambridge<br>International<br>A Level | Cambridge International Examinations Cambridge International Advanced Level | MANN, PADAC ANDRIAGE COM |

|---------------------------------------|-----------------------------------------------------------------------------|--------------------------|

| CANDIDATE<br>NAME                     |                                                                             |                          |

| CENTRE<br>NUMBER                      |                                                                             | CANDIDATE<br>NUMBER      |

|                                       |                                                                             | 0004/00                  |

**COMPUTING** 9691/33

Paper 3 October/November 2014

2 hours

Candidates answer on the Question Paper.

No additional materials are required.

No calculators allowed.

## **READ THESE INSTRUCTIONS FIRST**

Write your Centre number, candidate number and name on all the work you hand in.

Write in dark blue or black pen.

You may use a soft pencil for any diagrams, graphs or rough working.

Do not use staples, paper clips, glue or correction fluid.

DO **NOT** WRITE IN ANY BARCODES.

Answer all questions.

No marks will be awarded for using brand names for software packages or hardware.

At the end of the examination, fasten all your work securely together.

The number of marks is given in brackets [ ] at the end of each question or part question.

| (ii) | 3 * (x * y + 3) |   |

|------|-----------------|---|

|      | [               | 2 |

**(b)** Convert the following reverse Polish notation expressions into infix form.

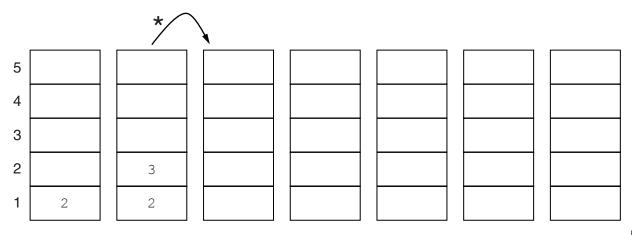

(c) An expression in reverse Polish notation can be evaluated on a computer system using a stack.

| (i) | Describe the operation of a stack. |

|-----|------------------------------------|

|     |                                    |

|     |                                    |

|     | [ <del>1</del>                     |

|     |                                    |

(ii) The expression in reverse Polish notation

is to be evaluated using a stack. The first available location on the stack is 1.

The diagram will show the changing contents of the stack as this expression is evaluated. Complete the diagram.

[4]

| (a) | Modern operating systems use a memory management technique called paging.  Explain how paging works by using the terms:         |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

|     | Explain how paging works by using the terms:                                                                                    |

|     | <ul><li>Page</li><li>Page frame</li><li>Page table</li></ul>                                                                    |

|     |                                                                                                                                 |

|     |                                                                                                                                 |

|     |                                                                                                                                 |

|     |                                                                                                                                 |

|     |                                                                                                                                 |

|     | [3]                                                                                                                             |

| (b) | For a computer system using multi-programming, the low-level scheduler decides what process will get next use of the processor. |

|     | One algorithm could be a "round-robin"; that is, every process gets use of the processor in sequence.                           |

|     | State <b>two</b> other algorithms which could be used by the low-level scheduler.                                               |

|     | 1                                                                                                                               |

|     |                                                                                                                                 |

|     | 2                                                                                                                               |

© UCLES 2014 [Turn over

www.PapaCambridge.com (c) For a "round-robin" algorithm, five processes are currently loaded and get the processor in the sequence:

PROG16 - PROGWP - PROGDB - PROG11 - PROG31, then return to PROG16

Process PROGDB has just completed its time-slice. Put the sequence of events below in the correct order.

Note: two of the statements will not be used.

| Α | Process PROG11                                                                             |

|---|--------------------------------------------------------------------------------------------|

| В | Interrupt received from the low-level scheduler                                            |

| С | Copy to the CPU registers the contents of the file directory for PROG11                    |

| D | Save the PC and all other registers contents for PROGDB to its Process Control Block (PCB) |

| Е | Copy to the CPU registers the contents of the stack                                        |

| F | Copy to the CPU registers the contents of the Process Control Block for PROG11             |

| List the sequence of events using the letters. |     |

|------------------------------------------------|-----|

|                                                |     |

|                                                |     |

|                                                |     |

|                                                |     |

|                                                | [4] |

www.PapaCambridge.com A database is to be set up to store data about paintings sold to customers by a galler Several attempts are made at the database design. (a) Consider Design 1: Customer(CustomerID, CustAddress, DateRegistered) Painting (PaintingID, Description, PaintingDate, Artist, Price) Sales(SalesID, CustomerID, PaintingID, PurchaseDate) Circle above the two foreign keys in this database design. [2] (ii) These two foreign keys form two relationships. Complete the entity-relationship (E-R) diagram to show them. [2] It is suggested that, as the number of sales made is relatively small, a SalesID is not required. The Sales table could be re-designed as: Sales(CustomerID, PurchaseDate, PaintingID) This design is to be implemented. How will this restrict the gallery's sales?

© UCLES 2014 [Turn over **(b)** More data is to be stored about the artist and the customer.

## Consider Design 2:

www.PapaCambridge.com Customer(CustomerID, CustomerName, CustAddress, DateRegistered) Painting(PaintingID, Description, PaintingDate, ArtistName, ArtistDateBorn, ArtistDateDied, ArtistNationality, Price) Sales(CustomerID, PurchaseDate, CustomerName, PaintingID)

| (i)  | Name the table which is not in Second Normal Form (2NF) and explain why.              |

|------|---------------------------------------------------------------------------------------|

|      | Table                                                                                 |

|      | Explanation                                                                           |

|      |                                                                                       |

|      |                                                                                       |

|      | Re-design this table.                                                                 |

|      | [3]                                                                                   |

| (ii) | Name the table which is not in Third Normal Form (3NF) and explain why.               |

|      | Table                                                                                 |

|      | Explanation                                                                           |

|      |                                                                                       |

|      |                                                                                       |

|      | Re-design this table and add a new table. Both these tables must be fully normalised. |

|      |                                                                                       |

|      |                                                                                       |

|      |                                                                                       |

|      | [5]                                                                                   |

(c) The final design for the customer table is:

| May May 1                                                                                 |

|-------------------------------------------------------------------------------------------|

| 7 The final design for the customer table is:                                             |

| The final design for the customer table is:                                               |

| Customer(CustomerID, CustomerName, CustAddress, TelNo, DateRegist                         |

| Customer 065 has contacted the gallery to tell them his new telephone number 0123 456789. |

| Write the Data Manipulation Language (DML) command to update their record.                |

|                                                                                           |

|                                                                                           |

|                                                                                           |

| [3]                                                                                       |

[Turn over © UCLES 2014

|                                                                                                                                                                                                           |                    |                           | general-pu |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|------------|--|

| sembly language instructions for a computer or (ACC), and an index register (IX).  Explanation                                                                                                            | Opcode<br>(binary) | Opcode (mnemonic) Operand |            |  |

| Direct addressing. Load the contents of the given address to ACC                                                                                                                                          | 0000 0100          | <address></address>       | LDD        |  |

| Load the given number to ACC                                                                                                                                                                              | 0000 0101          | <number></number>         | LDV        |  |

| Store the contents of ACC at the given address                                                                                                                                                            | 0001 0000          | <address></address>       | STO        |  |

| Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC                                                                                      | 0000 0110          | <address></address>       | LDI        |  |

| Indexed addressing. Form the address as <address +="" acc<="" address="" contents="" copy="" ix.="" of="" td="" the="" this="" to=""><td>0000 0111</td><td><address></address></td><td>LDX</td></address> | 0000 0111          | <address></address>       | LDX        |  |

| Add 1 to the contents of the register (ACC or IX)                                                                                                                                                         | 0000 0011          | <register></register>     | INC        |  |

| Output to the monitor the character corresponding to the ASCII character code in ACC                                                                                                                      | 1000 0001          |                           | OUTCH      |  |

| Input a denary number from the keyboard and store ACC                                                                                                                                                     | 1001 0000          |                           | IN         |  |

| Unconditional jump to the given address                                                                                                                                                                   | 1100 1000          | <address></address>       | JMP        |  |

| End the program and return to the operating system                                                                                                                                                        | 1111 1111          |                           | END        |  |

(a) (i) The instruction at address 102 is fetched.

|      | 9                                                                                        | ٠       |                                                      | cation 100.                                      |      |

|------|------------------------------------------------------------------------------------------|---------|------------------------------------------------------|--------------------------------------------------|------|

| The  | diagram shows a program loaded in main memory s                                          | tarting | at loc                                               | cation 100.                                      |      |

| Loc  | ations 200 onwards contain data which are used by the                                    | ne pro  | gram.                                                | Abrid                                            |      |

| (i)  | The instruction at address 102 is fetched.                                               |         |                                                      | 136                                              | ·co. |

|      | IX  Show the contents of the registers after execution. Write on the diagram to explain. | [2]     | 100<br>101<br>102<br>103<br>104<br>105<br>106<br>107 | LDI 150 OUTCH LDD 203 INC ACC STO 150 JP 100 END | 77   |

| (ii) | The instruction at address 100 is fetched.  ACC  IX                                      |         | 200<br>201<br>202<br>203<br>204<br>205               | 65<br>76<br>65<br>77<br>32<br>32                 |      |

Show the contents of the registers after execution.

Write on the diagram to explain.

[3]

**(b)** The given table of instructions shows the binary number used for each instruction's opcode.

All instructions in machine code are stored as a 16-bit pattern, with the opcode as the first 8 bits and the operand as the second 8 bits.

What is the maximum number of different instructions this processor could have?

(ii) Consider the instruction:

|   | _ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

Describe what this instruction does.

| <br>[2 |

|--------|

[Turn over © UCLES 2014

| (iii) | Programmers prefer to write machine code instructions in hexadecimal.                        | 1    |

|-------|----------------------------------------------------------------------------------------------|------|

|       | Programmers prefer to write machine code instructions in hexadecimal.  Explain why.          | 170  |

|       |                                                                                              | 1    |

|       |                                                                                              | [1]. |

| (iv)  | What is the hexadecimal number for the instruction shown in part (b)(ii)?                    |      |

| . ,   |                                                                                              | [1]  |

| Cha   |                                                                                              |      |

| Snc   | ow the machine code for the following instructions:                                          |      |

| (v)   | LDI 150                                                                                      |      |

|       |                                                                                              | [2]  |

| (vi)  | LDV 15                                                                                       |      |

|       |                                                                                              | [2]  |

| (vii) | A programmer makes the statement:                                                            |      |

|       | "For this instruction set, some of the instructions do not require an operand"               |      |

|       | Circle if this statement is true or false and explain with reference to the instructions giv | en.  |

|       | True / False                                                                                 |      |

|       |                                                                                              |      |

|       |                                                                                              |      |

|       |                                                                                              |      |

| Jse the ASCI    | I code table to | trace the first | four iteratio | <b>ns</b> of the given | program.  Decimal  82 |

|-----------------|-----------------|-----------------|---------------|------------------------|-----------------------|

| Character       | Decimal         | Character       | Decimal       | Character              | Decimal               |

| <space></space> | 32              | I               | 73            | R                      | 82                    |

| Α               | 65              | J               | 74            | S                      | 83                    |

| В               | 66              | K               | 75            | Т                      | 84                    |

| С               | 67              | L               | 76            | U                      | 85                    |

| D               | 68              | М               | 77            | V                      | 86                    |

| Е               | 69              | N               | 78            | W                      | 87                    |

| F               | 70              | 0               | 79            | Х                      | 88                    |

| G               | 71              | Р               | 80            | Υ                      | 89                    |

| Н               | 72              | Q               | 81            | Z                      | 90                    |

| ACC | Location<br>150 | OUTPUT |

|-----|-----------------|--------|

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

| 100 | LDI      | 150        |

|-----|----------|------------|

| 101 | OUTCH    |            |

| 102 | LDD      | 150        |

| 103 | INC      | ACC        |

| 104 | STO      | 150        |

| 105 | JP       | 100        |

| 106 | END      |            |

| 107 |          |            |

|     | <b> </b> | <i>ا</i> ا |

| 150 |          | 200        |

|     |          | 77         |

| 200 |          | 65         |

| 201 |          | 76         |

| 202 |          | 65         |

| 203 |          | 77         |

| 204 |          | 32         |

| 205 |          | 32         |

|     |          |            |

[5]

[Turn over © UCLES 2014

| Mos | st modern computers are designed using Von Neumann architecture.  Describe what is meant by Von Neumann architecture. |

|-----|-----------------------------------------------------------------------------------------------------------------------|

| (a) | Describe what is meant by Von Neumann architecture.                                                                   |

|     |                                                                                                                       |

|     |                                                                                                                       |

|     |                                                                                                                       |

|     | [2]                                                                                                                   |

| (b) | The sequence of operations below shows the fetch stage of the fetch-execute cycle in register transfer notation.      |

|     | 1. MAR ← [PC] 2. PC ← [PC] + 1 3. MDR ← [[MAR]] 4. CIR ← [MDR]                                                        |

|     | Note: [register] denotes the contents of the specified register.                                                      |

|     | Explain what is happening at the fetch stage.                                                                         |

|     | 1                                                                                                                     |

|     |                                                                                                                       |

|     |                                                                                                                       |

|     | 2                                                                                                                     |

|     |                                                                                                                       |

|     |                                                                                                                       |

|     | 3                                                                                                                     |

|     |                                                                                                                       |

|     |                                                                                                                       |

|     | 4                                                                                                                     |

|     |                                                                                                                       |

|             |             |      |                        | 13                                                                                                                             |

|-------------|-------------|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| (c)         | The         | ado  | dress bus and d        | ata bus are used during the fetch-execute cycle.                                                                               |

|             | (i)         | Na   | me another bus         | ata bus are used during the fetch-execute cycle.  sused in a typical microprocessor.                                           |

|             |             |      |                        |                                                                                                                                |

|             | (ii)        | Na   | me <b>one</b> signal o | carried by this bus.                                                                                                           |

|             |             |      |                        |                                                                                                                                |

|             |             |      |                        | [1]                                                                                                                            |

| (d)         | Cor         | side | er <b>two</b> assembly | / language instructions which were given in Question 4.                                                                        |

|             | Ins         | stru | ction                  |                                                                                                                                |

| Opc<br>mner | ode<br>noni | c)   | Operand                | Explanation                                                                                                                    |

|             | L           | DV   | <number></number>      | Load the given number to ACC                                                                                                   |

|             | L           | OD   | <address></address>    | Direct addressing. Load the contents of the given address to ACC                                                               |

|             | Cor         | side | er the following t     | two cases.                                                                                                                     |

|             |             | owir |                        | fetch stage, the instruction is decoded. The instruction is then executed ne address bus.                                      |

|             |             | owir | ng step 4 of the       | fetch stage, the instruction is decoded. Once decoded, the address a before the execution of the instruction can be completed. |

|             | For         | eac  | h instruction be       | low, circle either Case 1 or Case 2 and explain your choice.                                                                   |

|             | (i)         | LD'  | V 35                   |                                                                                                                                |

|             |             | Ca   | se 1 / Case 2          |                                                                                                                                |

|             |             | Ex   | planation              |                                                                                                                                |

|             |             |      |                        |                                                                                                                                |

|             |             |      |                        | [2]                                                                                                                            |

© UCLES 2014 [Turn over

(ii) LDD 35

Case 1 / Case 2

www.PapaCambridge.com The following are the first few lines of a source program written in a high-level language 6 about to be translated by the language compiler.

```

// invoicing program

// program written 21 Oct 2014

DECLARE i : INTEGER;

DECLARE Customer(40) : STRING;

DECLARE Address: STRING;

CONSTANT DiscountRate = 5;

// start of main program

CALL InitialiseCustomerData

REPEAT

...

...

```

| (a) | Dur   | ing the lexical analysis stage the compiler will use a keyword table and a symbol table | ÷.         |

|-----|-------|-----------------------------------------------------------------------------------------|------------|

|     | (i)   | Describe what information is contained in the keyword table.                            |            |

|     |       |                                                                                         |            |

|     |       |                                                                                         |            |

|     |       |                                                                                         | [2]        |

|     | (ii)  | List <b>three</b> entries which must be in the keyword table for this program.          |            |

|     |       |                                                                                         | [1]        |

|     | (iii) | Describe what information is contained in the symbol table.                             |            |

|     |       |                                                                                         |            |

|     |       |                                                                                         |            |

|     |       |                                                                                         | [2]        |

|     | (iv)  | List <b>three</b> entries which will be entered in the symbol table for this program.   | - <b>-</b> |

|     |       |                                                                                         |            |

|     | (v)  | Explain what happens during the lexical analysis stage of compilation. Including the keyword table and symbol table are used. |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------|

|     |      | 3                                                                                                                             |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      | [5]                                                                                                                           |

| (b) | The  | final stage of compilation is code optimisation.                                                                              |

|     | (i)  | Explain what is meant by code optimisation.                                                                                   |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      |                                                                                                                               |

|     |      | [2]                                                                                                                           |

|     | (ii) | Consider <b>three</b> assembly language instructions that were given in <b>Question 4</b> .                                   |

| Instru          | uction                | Funlanation                                                      |

|-----------------|-----------------------|------------------------------------------------------------------|

| Op Code Operand |                       | Explanation                                                      |

| LDD             | <address></address>   | Direct addressing. Load the contents of the given address to ACC |

| STO             | <address></address>   | Copy the contents of ACC to the given address                    |

| INC             | <register></register> | Add 1 to the contents of the register (ACC or IX)                |

Study the assembly language code below.

| 200 | LDD 151 |

|-----|---------|

| 201 | INC ACC |

| 202 | STO 151 |

| 203 | LDD 151 |

| 204 | INC ACC |

| 205 | STO 151 |

One instruction is not needed and could be removed during optimisation. State the address of this instruction.

Address of instruction .....[1]

© UCLES 2014

[Turn over

7 The function DateDiff is documented as follows:

FUNCTION DateDiff(Date1 : DATE, Date2 : DATE, OutputFlag : CHAR) RETURNS INT

The function assumes Date1 is earlier than Date2.

www.PapaCambridge.com The function calculates the difference, in days or as a whole number of months, between Date1 and Date2.

OutputFlag takes values:

- 'D': the result is computed and returned as a number of days

- 'M': the result is computed and returned as a whole number of months

An error is generated for each of the following:

- An unrecognised or missing flag parameter

- · A date parameter in the wrong format

- Date1 > = Date2

Dates are recognised by the function using the 'hash (#) delimiter'.

What is returned from the following function calls?

| (f) | High-level programming languages have two types of function. These are <b>built-in</b> and <b>user-defined</b> .  Explain the difference between them. You may give an example from your practical experience for a built-in function. |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (e) | DateDiff(#14/01/2014#, #17/01/2014#)[1]                                                                                                                                                                                                |

| (d) | DateDiff("12/09/2014", "15/09/2014", 'D')[1]                                                                                                                                                                                           |

| (c) | DateDiff(#30/07/2012#, #30/09/2012#, 'M')[1]                                                                                                                                                                                           |

| (b) | DateDiff(#21/10/2014#, #19/10/2014#, 'D')                                                                                                                                                                                              |

| (a) | DateDiff(#12/09/2014#, #15/09/2014#, 'D')[1]                                                                                                                                                                                           |

Permission to reproduce items where third-party owned material protected by copyright is included has been sought and cleared where possible. Every reasonable effort has been made by the publisher (UCLES) to trace copyright holders, but if any items requiring clearance have unwittingly been included, the publisher will be pleased to make amends at the earliest possible opportunity.

Cambridge International Examinations is part of the Cambridge Assessment Group. Cambridge Assessment is the brand name of University of Cambridge Local Examinations Syndicate (UCLES), which is itself a department of the University of Cambridge.